Product Summary

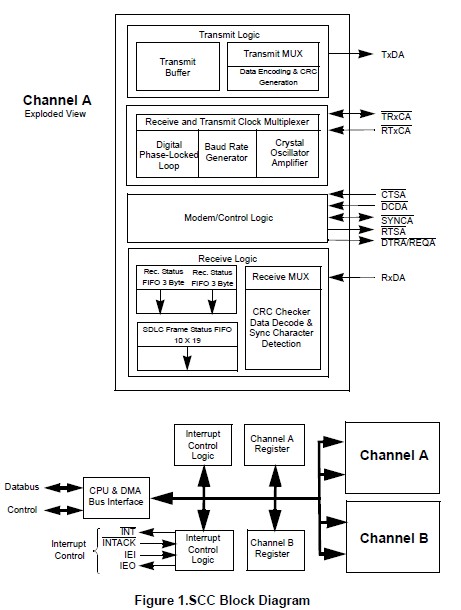

The Z85C3010VEC Serial Communications Controller (SCC), is a pin and software compatible CMOS member of the SCC family introduced by Zilog in 1981. It is a dualchannel, multiprotocol data communications peripheral that easily interfaces with CPU with either multiplexed or nonmultiplexed address/data buses. The Z85C3010VEC generates and checks CRC codes in any synchronous mode and can be programmed to check data integrity in various modes. The SCC also contains facilities for modem controls in both channels. In applications where these controls of Z85C3010VEC are not required, the modem controls can be used for general-purpose I/O. The daisy-chain interrupt hierarchy is also supported.

Parametrics

Z85C3010VEC absolute maximum ratings: (1)Vcc Supply Voltage range: –0.3 V to +7.0 V; (2)Voltages on all pins with respect to GND: –3 V to VCC +0.3 V; (3)Storage Temperature: –65℃ to +150℃.

Features

Z85C3010VEC features: (1)Z85C30: optimized for nonmultiplexed bus microprocessors; (2)Pin-compatible to NMOS versions; (3)Two independent 0 to 4.1 Mbps, full-duplex channels, each with separate crystal oscillator, Baud Rate Generator (BRG), and Digital Phase-Locked Loop (DPLL) for clock recovery; (4)features: Multiprotocol operation under program control; programmable for NRZ, NRZI or FM data encoding; (5)Asynchronous Mode with Five to Eight Bits and One, One and One-Half, or Two Stop Bits Per Character, Programmable Clock Factor, Break Detection and Generation; Parity, Overrun, and Framing Error Detection; (6)Synchronous Mode with Internal or External Character Synchronization on One or Two Synchronous Characters and CRC Generation and Checking with CRC-16 or CRC-CCITT Preset to either 1s or 0s; (7)SDLC/HDLC Mode with Comprehensive Frame-Level Control, Automatic Zero Insertion and Deletion, I-Field Residue Handling, Abort Generation and Detection, CRC Generation and Checking, and SDLC Loop; (8)Software Interrupt Acknowledge Feature (not available with NMOS); (9)Local Loopback and Auto Echo Modes; (10)Supports T1 Digital Trunk2; (11)Enhanced DMA Support (not available with NMOS) 10 x 19-Bit Status FIFO 14-Bit Byte Counter; (12)Speeds: Z85C3O: 8.5, 10, 16.384 MHz.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

Z85C3010VEC |

ZiLOG |

I/O Controller Interface IC 10 MHz Z8500 CMOS XT |

Data Sheet |

Negotiable |

|

||||

|

Z85C3010VEC00TR |

|

IC Z8500 SCC 44PLCC |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))